# **1547.1**<sup>™</sup>

IEEE Standard Conformance Test Procedures for Equipment Interconnecting Distributed Resources with Electric Power Systems

### **IEEE Standards Coordinating Committee 21**

Sponsored by the IEEE Standards Coordinating Committee 21 on Fuel Cells, Photovoltaics, Dispersed Generation, and Energy Storage

3 Park Avenue, New York, NY 10016-5997, USA

1 July 2005 Print: SH95346 PDF: SS95346

# **IEEE Standard Conformance Test Procedures for Equipment Interconnecting Distributed Resources with Electric Power Systems**

Sponsor

**IEEE Standards Coordinating Committee 21 on** Fuel Cells, Photovoltaics, Dispersed Generation, and Energy Storage

Approved 9 June 2005

Reaffirmed 16 June 2011

#### IEEE-SA Standards Board

Abstract: This standard specifies the type, production, and commissioning tests that shall be performed to demonstrate that the interconnection functions and equipment of the distributed resources (DR) conform to IEEE Std 1547™.

Keywords: distributed resources, interconnection, test procedures

Copyright © 2005 by the Institute of Electrical and Electronics Engineers, Inc. All rights reserved. Published 1 July 2005. Printed in the United States of America.

IEEE is a registered trademark in the U.S. Patent & Trademark Office, owned by the Institute of Electrical and Electronics Engineers, Incorporated.

ISBN 0-7381-4736-2 SH95346 Print: ISBN 0-7381-4737-0 SS95346 PDF:

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.

The Institute of Electrical and Electronics Engineers, Inc. 3 Park Avenue, New York, NY 10016-5997, USA

**IEEE Standards** documents are developed within the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association (IEEE-SA) Standards Board. The IEEE develops its standards through a consensus development process, approved by the American National Standards Institute, which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members of the Institute and serve without compensation. While the IEEE administers the process and establishes rules to promote fairness in the consensus development process, the IEEE does not independently evaluate, test, or verify the accuracy of any of the information or the soundness of any judgments contained in its standards.

Use of an IEEE Standard is wholly voluntary. The IEEE disclaims liability for any personal injury, property or other damage, of any nature whatsoever, whether special, indirect, consequential, or compensatory, directly or indirectly resulting from the publication, use of, or reliance upon this, or any other IEEE Standard document.

The IEEE does not warrant or represent the accuracy or content of the material contained herein, and expressly disclaims any express or implied warranty, including any implied warranty of merchantability or fitness for a specific purpose, or that the use of the material contained herein is free from patent infringement. IEEE Standards documents are supplied "AS IS."

The existence of an IEEE Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard. Every IEEE Standard is subjected to review at least every five years for revision or reaffirmation, or every ten years for stabilization. When a document is more than five years old and has not been reaffirmed, or more than ten years old and has not been stabilized, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE Standard.

In publishing and making this document available, the IEEE is not suggesting or rendering professional or other services for, or on behalf of, any person or entity. Nor is the IEEE undertaking to perform any duty owed by any other person or entity to another. Any person utilizing this, and any other IEEE Standards document, should rely upon his or her independent judgment in the exercise of reasonable care in any given circumstances or, as appropriate, seek the advice of a competent professional in determining the appropriateness of a given IEEE standard.

Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of IEEE, the Institute will initiate action to prepare appropriate responses. Since IEEE Standards represent a consensus of concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration. A statement, written or oral, that is not processed in accordance with the IEEE-SA Standards Board Operations Manual shall not be considered the official position of IEEE or any of its committees and shall not be considered to be, nor be relied upon as, a formal interpretation of the IEEE. At lectures, symposia, seminars, or educational courses, an individual presenting information on IEEE standards shall make it clear that his or her views should be considered the personal views of that individual rather than the formal position, explanation, or interpretation of the IEEE.

Comments for revision of IEEE Standards are welcome from any interested party, regardless of membership affiliation with IEEE. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Recommendations to change the status of a stabilized standard should include a rationale as to why a revision or withdrawal is required. Comments and recommendations on standards, and requests for interpretations should be addressed to:

Secretary, IEEE-SA Standards Board 445 Hoes Lane Piscataway, NJ 08854-4141 USA

Authorization to photocopy portions of any individual standard for internal or personal use is granted by The Institute of Electrical and Electronics Engineers, Inc., provided that the appropriate fee is paid to Copyright Clearance Center. To arrange for payment of licensing fee, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; +1 978 750 8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

### Introduction

This introduction is not part of IEEE Std 1547.1-2005, IEEE Standard Conformance Test Procedures for Equipment Interconnecting Distributed Resources with Electric Power Systems.

IEEE Std 1547.1 is one of a series of standards developed by Standards Coordinating Committee 21 (SCC21) concerning distributed resources (DR) interconnection. The titles of the additional documents in that series follow:

- IEEE Std 1547, IEEE Standard for Interconnecting Distributed Resources with Electric Power Systems<sup>a</sup>

- IEEE P1547.2<sup>™</sup>, Draft Application Guide for IEEE Std 1547, Interconnecting Distributed Resources with Electric Power Systems [B6]<sup>b</sup>

- IEEE P1547.3<sup>™</sup>, Draft Guide for Monitoring, Information Exchange, and Control of Distributed Resources Interconnected with Electric Power Systems [B7]

- IEEE P1547.4<sup>™</sup>, Draft Guide for Design, Operation, and Integration of Distributed Resource Island Systems with Electric Power Systems [B8]

- IEEE P1547.5<sup>™</sup>, Draft Technical Guidelines for Interconnection of Electric Power Sources Greater Than 10 MVA to the Power Transmission Grid [B9]

- IEEE P1547.6<sup>TM</sup>, Draft Recommended Practice for Interconnecting Distributed Resources with Electric Power Systems Distribution Secondary Networks [B10]

The root standard, IEEE Std 1547, defines a set of uniform requirements for the interconnection of DR to the distribution segment of the electric power system (EPS). IEEE Std 1547 is an outgrowth of the changes in the environment for production and delivery of electricity and builds on prior IEEE recommended practices and guidelines developed by SCC21.

IEEE Std 1547 includes requirements relevant to the operation of the interconnection. It generally defines limitations and set points for various parameters that must be satisfied prior to the connection of a DR unit to the EPS, at the instant of connection, and for the separation of such resources from the EPS for abnormal conditions.

IEEE Std 1547.1 provides conformance test procedures to establish and verify compliance with the requirements of IEEE Std 1547. When applied, the IEEE 1547.1 test procedures can provide a means for manufacturers, utilities, or independent testing agencies to confirm the suitability of any given interconnection system (ICS) or component intended for use in the interconnection of DR with the EPS. Such certification can lead to the ready acceptance of confirmed equipment as suitable for use in the intended service by the parties concerned. While this standard defines test procedures, it does not specify measurement techniques. Suitable measurement techniques can be found in various technical publications including, but not limited to, IEEE Std 120<sup>™</sup> [B13].

It is beyond the scope of IEEE 1547.1 to specify the design and performance criteria for ICSs or components. It is left to the parties concerned to determine that the equipment manufacturer's specifications and confirmed performance satisfy the technical needs of the EPS distribution circuit to which the DR unit is to be connected. Similarly, this standard does not address the local electrical power system technical needs nor load requirements for the facility or premises where the point of DR connection is made.

<sup>&</sup>lt;sup>a</sup>Information on references can be found in Clause 2.

<sup>&</sup>lt;sup>b</sup>The numbers in brackets correspond to the numbers of the bibliography in Annex B.

#### Notice to users

#### Errata

Errata, if any, for this and all other standards can be accessed at the following URL: <u>http://</u><u>standards.ieee.org/reading/ieee/updates/errata/index.html.</u> Users are encouraged to check this URL for errata periodically.

#### Interpretations

Current interpretations can be accessed at the following URL: <u>http://standards.ieee.org/reading/ieee/interp/index.html.</u>

#### Patents

Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. The IEEE shall not be responsible for identifying patents or patent applications for which a license may be required to implement an IEEE standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

#### Participants

At the time this standard was completed, the SCC21 had the following membership:

#### **Richard DeBlasio**, *Chair* **Steve Chalmers**, *Vice Chair* **Thomas S. Basso**, *Secretary*

Jerry Anderson Jay Chamberlin James M. Daley Douglas C. Dawson William E. Feero N. Richard Friedman Frank Goodman Kelvin Hecht Barry Hornberger Joseph L. Koepfinger Benjamin Kroposki Robert McConnell John Stevens John Wiles John Wohlgemuth Timothy P. Zgonena

At the time this standard was completed, the DR Interconnection Conformance Test Procedures Working Group (P1547.1 WG) of the SCC21 had the following membership. These members also composed the individual balloting committee that voted on this standard. Balloters may have voted for approval, disapproval, or abstention.

#### James M. Daley, *Chair* Charles Whitaker, *Vice Chair* Benjamin Kroposki, *Secretary*

William J. Ackerman J. Reese Adomaitis Brij Aggarwal Paul Barnhart David Bassett Thomas Basso Michael Behnke Vijay Bhavaraju Kenneth Birt William Brooks Gary Brownfield Ted Burse Eldridge R Byron Simon Cheng Keith Chow Stephen P. Conrad Terry Conrad William Cook Dave M. Costyk Matthew Davis Richard DeBlasio Joseph Debs Guru Dutt Dhingra Kevin Donahoe Neil Dowling Michael Edds Lynnda Ell Doug Edwards Gary R. Engmann Thomas (Tom) W. Ernst William E. Feero David Frank N. Richard (Dick) Friedman Joseph (Joe) Galdo Andris Garsils S. (Dave) Gohil Manuel Gonzalez Frank Goodman Tom Gordon Randall Groves Nancy Gunderson James Gurnev Ronald D. Hartzel Steven Hensley Clark G. Hochgraf Donald L. Hornak Raymond M. Hudson Michael J. Hyland Steven Jochums Vinod John John R. Kennedy Yuri Khersonsky Joseph L. Koepfinger Scott Lacy

Frank Lambert Richard (Rick) Langley Gerald Lee James W. Lemke David Lemmerman Jason Lin Guoliang Liu Kevin Loving Vahid Madani Scott Malinowski Sylvain Martel Frank Mayle Anthony Mazy Walter McCannon Peter McNutt Nigel McOuin G. Michel Anne Morgan Charles Morse Pratap Mysore Arun Narang T. W. Olsen Gary Olson Gregory Olson Ronald Onate Miklos Orosz Michael Pehosh Lisa Potter Stan Pukash Robert Rallo Charles Rogers

**Bob Saint** Carl Schneider Gary W. Scott Gary Seifert Kent Sheldon H. Jin Sim Andrew Skok Cameron Smallwood Dehn Stevens David Stone Paul Sullivan Craig Taborsky Chand Tailor Rao Thallam Elisabeth (Betty) A. Tobin Mohammad Vaziri Hemant Vora Tim (Carl T.) Wall Simon Wall Reigh A. Walling Randall (Randy) West Ron Westfall John S. Wheat John Wiles Robert Wills Thomas Wind Zhihong Ye Timothy P. Zgonena Donald (Don) W. Zipse Ahmed Zobaa

The following working group members participated in finalizing the development of this standard with working group inputs and in facilitating the development of those inputs throughout the standards development process:

James M. Daley Benjamin Kroposki Richard Langley Kevin Loving Gary L. Olson Charles Whitaker Timothy P. Zgonena

When the IEEE-SA Standards Board approved this standard on 9 June 2005, it had the following membership:

#### Steve M. Mills, Chair Richard H. Hulett, Vice Chair Don Wright, Past Chair Judith Gorman, Secretary

Mark D. Bowman Dennis B. Brophy Joseph Bruder Richard Cox Bob Davis Julian Forster\* Joanna N. Guenin Mark S. Halpin Raymond Hapeman

\*Member Emeritus

th Gorman, Secretar William B. Hopf Lowell G. Johnson Herman Koch Joseph L. Koepfinger\* David J. Law Daleep C. Mohla Paul Nikolich

T. W. Olsen Glenn Parsons Ronald C. Petersen Gary S. Robinson Frank Stone Malcolm V. Thaden Richard L. Townsend Joe D. Watson Howard L. Wolfman Also included are the following nonvoting IEEE-SA Standards Board liaisons:

Satish K. Aggarwal, *NRC Representative* Richard DeBlasio, *DOE Representative* Alan H. Cookson, *NIST Representative*

> Michelle D. Turner IEEE Standards Project Editor

### Contents

| 1.                  | Over               | Overview1                                                                     |      |  |  |

|---------------------|--------------------|-------------------------------------------------------------------------------|------|--|--|

|                     | 1.1                | Scope                                                                         | 1    |  |  |

|                     | 1.2                | Purpose                                                                       | 1    |  |  |

|                     | 1.3                | Limitations                                                                   |      |  |  |

| 2.                  | Norn               | native references                                                             | 2    |  |  |

| 3.                  | Defir              | Definitions and acronyms                                                      |      |  |  |

|                     | 3.1                | ICS boundaries                                                                | 3    |  |  |

|                     | 3.2                | Definitions                                                                   |      |  |  |

|                     | 3.3                | Acronyms                                                                      |      |  |  |

| 4.                  | Gene               | General requirements                                                          |      |  |  |

|                     | 4.1                | Test result accuracy                                                          | 5    |  |  |

|                     | 4.2                | Testing environment                                                           |      |  |  |

|                     | 4.3                | Measurement accuracy and calibration of the testing equipment                 |      |  |  |

|                     | 4.4                | Product information                                                           |      |  |  |

|                     | 4.5                | Test reports                                                                  |      |  |  |

|                     | 4.6                | Testing equipment requirements                                                |      |  |  |

| 5. Type tests       |                    | tests                                                                         | 7    |  |  |

|                     | 5.1                | Temperature stability                                                         | 8    |  |  |

|                     | 5.2                | Test for response to abnormal voltage conditions                              |      |  |  |

|                     | 5.3                | Response to abnormal frequency conditions                                     |      |  |  |

|                     | 5.4                | Synchronization                                                               |      |  |  |

|                     | 5.5                | Interconnection integrity                                                     |      |  |  |

|                     | 5.6                | Limitation of dc injection for inverters without interconnection transformers |      |  |  |

|                     | 5.7                | Unintentional islanding                                                       |      |  |  |

|                     | 5.8                | Reverse power (for unintentional islanding)                                   |      |  |  |

|                     | 5.9                | Open phase                                                                    |      |  |  |

|                     | 5.10               | Reconnect following abnormal condition disconnect                             |      |  |  |

|                     | 5.11               | Harmonics                                                                     |      |  |  |

|                     |                    | Flicker                                                                       |      |  |  |

| 6. Production tests |                    | action tests                                                                  | . 38 |  |  |

|                     | 6.1                | Response to abnormal voltage                                                  | . 39 |  |  |

|                     | 6.2                | Response to abnormal frequency                                                |      |  |  |

|                     | 6.3                | Synchronization                                                               |      |  |  |

|                     | 6.4                | Documentation                                                                 |      |  |  |

| 7.                  | Commissioning test |                                                                               |      |  |  |

|                     | 7.1                | General                                                                       | . 41 |  |  |

|                     | 7.2                | Verifications and inspections                                                 |      |  |  |

|                     | 7.2                | Field-conducted type and production tests                                     |      |  |  |

|                     | 7.4                | Unintentional islanding functionality test.                                   |      |  |  |

|                     | /+                 | Connectional Islanding functionality test                                     | · 74 |  |  |

|                                  |         | Cease-to-energize functionality test<br>Revised settings |    |  |

|----------------------------------|---------|----------------------------------------------------------|----|--|

| 8.                               | Period  | odic interconnection tests                               |    |  |

| Annex A (normative) Test signals |         |                                                          |    |  |

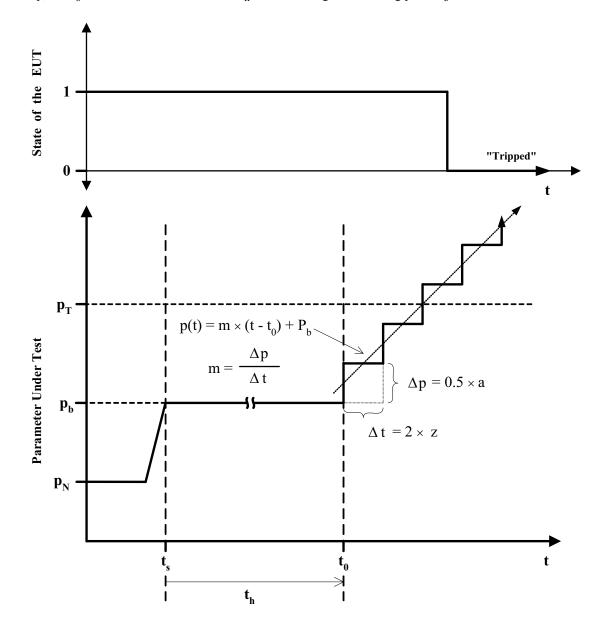

|                                  | A.      | 1 Magnitude test (ramp function)—general                 | 45 |  |

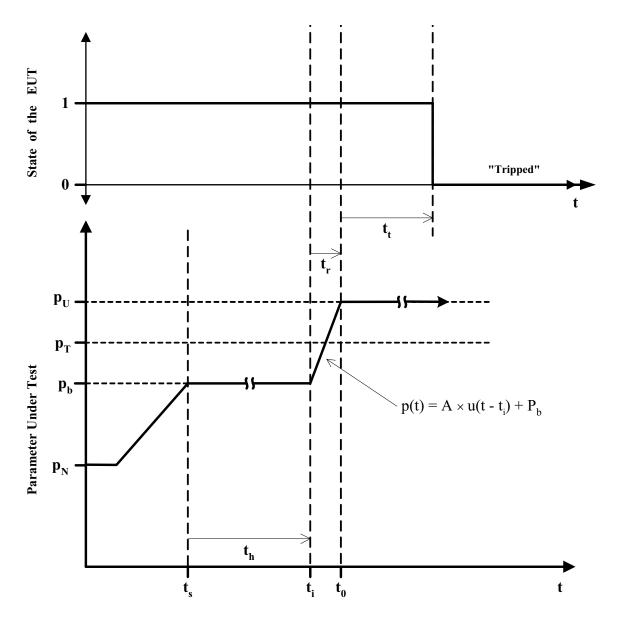

|                                  | A.2     | 2 Time test (step function)—general                      | 48 |  |

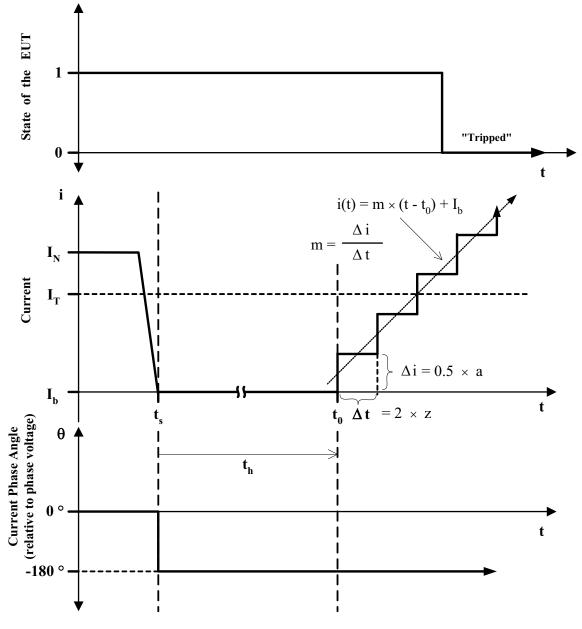

|                                  | Α.      | 3 Reverse-power magnitude test (ramp function)           | 48 |  |

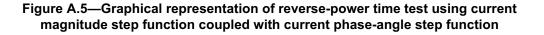

|                                  | A.4     | 4 Reverse-power time test (step function)                | 50 |  |

| Annex                            | P (info | ormative) Bibliography                                   | 53 |  |

### IEEE Standard Conformance Test Procedures for Equipment Interconnecting Distributed Resources with Electric Power Systems

#### 1. Overview

This standard provides tests and procedures for verifying conformance of interconnection systems (ICSs) to IEEE Std 1547<sup>TM</sup>.<sup>1</sup> It is recognized that an ICS can be a single device providing all required functions or an assembly of components, each having limited functions. Components having limited functions shall be tested for those functions in accordance with this standard. Conformance may be established through combination of type (referred to as "design" tests in IEEE Std 1547), production, and commissioning tests. Additionally, conformance to IEEE Std 1547 requires interconnection installation evaluation and periodic tests.

This standard also includes Annex A, which describes test signals and ramp functions used in conducting some tests. Additionally, a bibliography is included as Annex B; it lists documents that are referred to in this standard for informative purposes, but that are not required to implement the procedures defined in this standard.

#### 1.1 Scope

This standard specifies the type, production, and commissioning tests that shall be performed to demonstrate that the interconnection functions and equipment of the distributed resources (DR) conform to IEEE Std 1547.

#### 1.2 Purpose

Interconnection equipment that connects DR to an electric power system (EPS) must meet the requirements specified in IEEE Std 1547. Standardized test procedures are necessary to establish and verify compliance with those requirements. These test procedures must provide both repeatable results, independent of test location, and flexibility to accommodate the variety of DR technologies.

<sup>&</sup>lt;sup>1</sup>Information on references can be found in Clause 2.

#### 1.3 Limitations

This standard does not cover testing for safety.

Although this standard does not define a certification process, these tests may be used as part of such a process.

#### 2. Normative references

The following referenced documents are indispensable for the application of this standard. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments or corrigenda) applies.

The applicability of the following standards is determined by the specific requirements stated in this standard, such as requiring certain sections.

ANSI C37.06, American National Standard for AC High-Voltage Circuit Breakers Rated on a Symmetrical Current Basis—Preferred Ratings and Related Required Capabilities.<sup>2</sup>

ANSI C84.1, American National Standard for Electric Power Systems and Equipment—Voltage Ratings (60 Hz).

IEEE C37.09<sup>™</sup>, IEEE Standard Test Procedure for AC High-Voltage Circuit Breakers Rated on a Symmetrical Current Basis.<sup>3, 4</sup>

IEEE Std C37.90.1<sup>™</sup>, IEEE Standard for Surge Withstand Capability (SWC) Tests for Relays and Relay Systems Associated with Electric Power Apparatus.

IEEE Std C37.90.2<sup>TM</sup>, IEEE Standard for Withstand Capability of Relay Systems to Radiated Electromagnetic Interference from Transceivers.

IEEE Std C62.41.2<sup>TM</sup>, IEEE Recommended Practice on Characterization of Surges in Low-Voltage (1000 V and Less) AC Power Circuits.

IEEE Std C62.45<sup>TM</sup>, IEEE Recommended Practice on Surge Testing for Equipment Connected to Low-Voltage (1000 V and Less) AC Power Circuits.

IEEE Std 1547<sup>™</sup>, IEEE Standard for Interconnecting Distributed Resources with Electric Power Systems.

NEMA MG-1, Motors and Generators.<sup>5</sup>

<sup>&</sup>lt;sup>2</sup>ANSI publications are available from the Sales Department, American National Standards Institute, 25 West 43rd Street, 4th Floor, New York, NY 10036, USA (http://www.ansi.org/).

<sup>&</sup>lt;sup>3</sup>IEEE publications are available from the Institute of Electrical and Electronics Engineers, 445 Hoes Lane, Piscataway, NJ 08854, USA (http://standards.ieee.org/).

<sup>&</sup>lt;sup>4</sup>The IEEE standards or products referred to in this clause are trademarks of the Institute of Electrical and Electronics Engineers, Inc. <sup>5</sup>NEMA publications are available from Global Engineering Documents, 15 Inverness Way East, Englewood, Colorado 80112, USA (http://global.ihs.com/).

#### 3. Definitions and acronyms

For purposes of this standard, the following terms and definitions apply. *The Authoritative Dictionary of IEEE Standards Terms* [B5] should be referenced for terms not defined in this clause.

#### 3.1 ICS boundaries

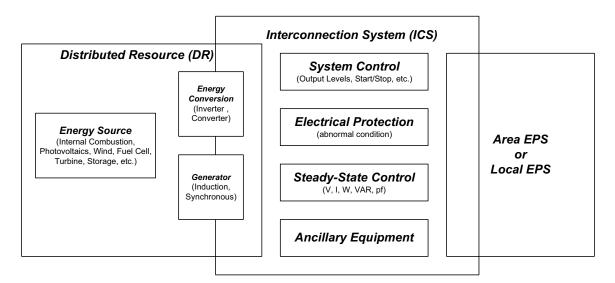

An ICS consists of system controls, electrical protection, and steady-state control and may include energy conversion and/or generator. The DR may include all or part of the ICS. Figure 1 shows the boundary between the ICS, the EPS, and the energy source.

Figure 1—Boundaries between the ICS, the EPS, and the DR

#### 3.2 Definitions

**3.2.1 area electric power system (EPS):** An EPS that serves local EPSs. Note that, typically, an area EPS has primary access to public rights-of-way, priority crossing of property boundaries, etc., and is subject to regulatory oversight.

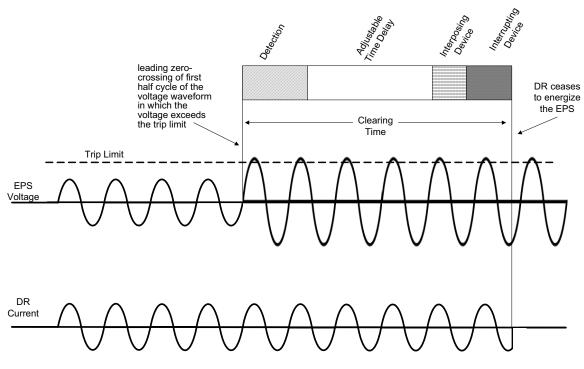

**3.2.2 clearing time:** The time between the start of the abnormal condition and the distributed resources' (DR's) ceasing to energize the area electric power system (EPS). It is the sum of the detection time, any adjustable time delay, the operating time for any interposing devices (if used), and the operating time for the interrupting device (used to interconnect the DR with the area EPS).

**3.2.3 commissioning test:** A test conducted when the equipment is installed to verify correct operation.

3.2.4 design test: See: type test.

**3.2.5 detection time:** The minimum length of time from the inception of the abnormal condition to the change in state of the device or function dedicated to controlling the interrupting device. *Syn:* processing time.

**3.2.6 distributed generation (DG):** Electric generation facilities connected to an area electric power system (EPS) through a point of common coupling (PCC); a subset of distributed resources (DR).

Copyright © 2005 IEEE. All rights reserved.

**3.2.7 distributed resources (DR):** Sources of electric power that are not directly connected to a bulk power transmission system. DR includes both generators and energy storage technologies.

**3.2.8 electric power system (EPS):** Facilities that deliver electric power to a load. Note that EPS may include generation units. *See also:* area electric power system (EPS); local electric power system (EPS).

**3.2.9 interconnection system (ICS):** the collection of all equipment and functions, taken as a group, used to interconnect a distributed resources (DR) unit to an area electric power system (EPS).

**3.2.10 interrupting device:** A device capable of being opened and reclosed whose purpose is to interrupt faults and restore service or disconnect loads. These devices can be manual, automatic, or motor-operated. Examples include circuit breakers, motor-operated switches, and electronic switches.

**3.2.11 inverter:** A machine, device, or system that changes dc power to ac power.

**3.2.12 island:** A condition in which a portion of an area electric power system (EPS) is energized solely by one or more local EPSs through the associated points of common coupling (PCCs) while that portion of the area EPS is electrically separated from the rest of the area EPS.

**3.2.13 local electric power system (EPS):** An EPS contained entirely within a single premises or group of premises.

**3.2.14 nominal:** The value or range of a parameter being within expected norms or being the normal operating level of that parameter.

**3.2.15 paralleling device:** A device (e.g., circuit breaker) operating under the control of a synchronizing function to electrically connect two energized power sources together.

**3.2.16 point of common coupling (PCC):** The point where a local electric power system (EPS) is connected to an area EPS.

**3.2.17 point of distributed resources (DR) connection:** The point where a DR unit is electrically connected in an electric power system (EPS).

**3.2.18 production test:** A test conducted on every unit of equipment prior to shipment.

**3.2.19 signal injection test methods:** Test methods where signals are injected into the sense terminals of the equipment under test (EUT). These methods include both primary injection test methods and secondary injection test methods.

**3.2.20 simulated area electric power system (EPS):** An assembly of voltage and frequency test equipment replicating a utility power source. Where appropriate, the actual area EPS can be used as the simulated area EPS.

3.2.21 simulated utility: See: simulated area electric power system (EPS).

**3.2.22 total rated-current distortion (TRD):** The total root-sum-square of the current harmonics created by the distributed resources (DR) unit operating into a linear balanced load divided by the greater of the test load current demand IL or the rated-current capacity of the DR unit Irated.

**3.2.23 trip time:** The interval that begins at the leading zero-crossing of the first half cycle of the voltage waveform in which the measured parameter (e.g., frequency, voltage, power) exceeds the trip limit and ends when the equipment under test (EUT) responds as required.

**3.2.24 type test:** Test of one or more devices made to a certain design to demonstrate that the design meets certain specifications. *Syn:* design test.

#### 3.3 Acronyms

| d.p.f.displacement power factorDRdistributed resourcesEMIelectromagnetic interferenceEPSelectric power systemEUTequipment under testICSinterconnection systemPCCpoint of common couplingp.f.power factorPUTparameter under testRLCresistance, inductance, and capacitancermsroot mean squareTHDtotal harmonic distortionVTvoltage transformer | CT     | current transformer                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------|

| EMIelectromagnetic interferenceEMIelectric power systemEUTequipment under testEUTinterconnection systemPCCpoint of common couplingp.f.power factorPUTparameter under testRLCresistance, inductance, and capacitancermsroot mean squareTHDtotal harmonic distortionRLDtotal nated-current distortion                                           | d.p.f. | displacement power factor               |

| EPSelectric power systemEUTequipment under testICSinterconnection systemPCCpoint of common couplingp.f.power factorPUTparameter under testRLCresistance, inductance, and capacitancermsroot mean squareTHDtotal harmonic distortionRLDtotal nated-current distortion                                                                          | DR     | distributed resources                   |

| EUTequipment under testICSinterconnection systemPCCpoint of common couplingp.f.power factorPUTparameter under testRLCresistance, inductance, and capacitancermsroot mean squareTHDtotal harmonic distortionTRDtotal rated-current distortion                                                                                                  | EMI    | electromagnetic interference            |

| ICSinterconnection systemPCCpoint of common couplingp.f.power factorPUTparameter under testRLCresistance, inductance, and capacitancermsroot mean squareTHDtotal harmonic distortionTRDtotal rated-current distortion                                                                                                                         | EPS    | electric power system                   |

| PCCpoint of common couplingp.f.power factorPUTparameter under testRLCresistance, inductance, and capacitancermsroot mean squareTHDtotal harmonic distortionTRDtotal rated-current distortion                                                                                                                                                  | EUT    | equipment under test                    |

| p.f.power factorPUTparameter under testRLCresistance, inductance, and capacitancermsroot mean squareTHDtotal harmonic distortionTRDtotal rated-current distortion                                                                                                                                                                             | ICS    | interconnection system                  |

| PUTparameter under testPUTparameter under testRLCresistance, inductance, and capacitancermsroot mean squareTHDtotal harmonic distortionTRDtotal rated-current distortion                                                                                                                                                                      | PCC    | point of common coupling                |

| RLCresistance, inductance, and capacitancermsroot mean squareTHDtotal harmonic distortionTRDtotal rated-current distortion                                                                                                                                                                                                                    | p.f.   | power factor                            |

| rmsroot mean squareTHDtotal harmonic distortionTRDtotal rated-current distortion                                                                                                                                                                                                                                                              | PUT    | parameter under test                    |

| THDtotal harmonic distortionTRDtotal rated-current distortion                                                                                                                                                                                                                                                                                 | RLC    | resistance, inductance, and capacitance |

| TRD total rated-current distortion                                                                                                                                                                                                                                                                                                            | rms    | root mean square                        |

|                                                                                                                                                                                                                                                                                                                                               | THD    | total harmonic distortion               |

| VT voltage transformer                                                                                                                                                                                                                                                                                                                        | TRD    | total rated-current distortion          |

|                                                                                                                                                                                                                                                                                                                                               | VT     | voltage transformer                     |

#### 4. General requirements

Implementation of these test procedures shall be conducted in accordance with appropriate safety procedures, sequences, and precautions.

#### 4.1 Test result accuracy

The test results shall verify that the equipment under test (EUT) meets the requirements of IEEE Std 1547 within the manufacturer's specified accuracy.

#### 4.2 Testing environment

The manufacturer shall specify the range of environmental conditions for the EUT. Therefore, tests shall be conducted in an environment that is within the manufacturer's specified environmental operating conditions.

#### 4.3 Measurement accuracy and calibration of the testing equipment

Measurement equipment used to confirm performance of an EUT shall have calibration traceablity. The accuracy of the measuring equipment shall be suitable for the test being conducted.

Copyright © 2005 IEEE. All rights reserved.

#### 4.4 Product information

The setting of limits and the structure of this standard are based on the understanding that the installer and user are responsible for following the installation recommendations of the manufacturer.

The manufacturer shall supply the EUT tester with documentation necessary for the correct installation into a typical system or process in the intended environment. A functional description and a definition of specification limits for the acceptance criteria shall be provided by the manufacturer and noted in the test report.

Any external devices or equipment or special connection requirements necessary to conduct the tests shall be clearly stated (including rationale) in the user documentation. Special requirements can include the amount of network impedance, voltampere burden of the EUT, the use of shielded or special cables, maximum cable length, the use of filters, and the correct bonding to functional earth (grounding). If different devices or connection requirements apply in different environments, this shall also be stated. A list of auxiliary equipment (e.g., options or enhancements) that can be added to the EUT and that can impact the result of EUT tests shall be made available. This information shall also be covered in the test report to clarify the as-tested arrangement(s).

Accuracy and tolerances of device parameters shall be stated by the manufacturers.

#### 4.5 Test reports

The test results shall be documented in a test report. The report shall clearly and unambiguously present all relevant information of the tests (e.g., load conditions, conductor type or routing, functional description, acceptance criteria).

Within the test report, test procedures, as performed, shall be detailed; and engineering considerations, including test modifications and exemptions, shall be justified. When used in conjunction with this standard, the test report shall include sufficient critical operating information to rerun the test and reproduce the results.

Each test method shall be specified; and engineering considerations, including range of operating conditions, shall be justified.

#### 4.6 Testing equipment requirements

#### 4.6.1 Simulated area EPS (utility) source requirements

Where testing allows the use of a simulated area EPS source, the following requirements shall be met:

- The simulated area EPS source shall be capable of confirming the manufacturer's stated performance.

- The voltage harmonics of the simulated area EPS source shall be less than 2.5% total harmonic distortion (THD).

- The individual voltage harmonics of the simulated utility shall be less than 50% of the limits in Table 3 of IEEE Std 1547.

- During the tests, the steady-state voltage of the simulated area EPS source shall not vary by more than  $\pm 1\%$  of the nominal voltage.

- For voltage trip magnitude tests, the voltage change resolution of the simulated utility source shall be within 0.5*a* of the nominal voltage, where *a* is the manufacture's stated accuracy.

- For frequency trip magnitude tests, the frequency change resolution of the simulated utility source shall be within 0.5*a* of the nominal frequency, where *a* is the manufacture's stated accuracy.

- The number of phase and neutral connections provided by simulated area EPS shall be compatible with the EUT. A multiphase simulated area EPS that provides a neutral connection shall produce phase-to-neutral voltages that are balanced within  $\pm$  3% of nominal and phase displacement to within  $\pm$  3°. For multiphase simulated area EPSs without a neutral connection, the phase-to-phase voltage balance shall be  $\pm$  3% of nominal in magnitude.

- For voltage trip timing tests, the simulated utility source shall be capable of a step change from  $V_1$  to  $V_1 + 0.5(V_2 V_1)$  within the greater of one cycle of the voltage waveform or 1% of the trip time setting of the EUT.<sup>6</sup>

- For frequency trip timing tests, the simulated utility source shall be capable of a step change from  $f_1$  to  $f_1 + 0.5(f_2 f_1)$  within the greater of one cycle of the voltage waveform or 1% of the trip time setting of the EUT.<sup>7</sup>

#### 4.6.2 Measurement system requirements

Each measurement shall have an uncertainty of no more than 0.5 times the accuracy of the EUT. Measurement equipment shall be capable of confirming the manufacturer's stated performance.

#### 5. Type tests

Type tests are performed on a representative unit and may be conducted in the factory, at a testing laboratory, or on equipment in the field. Unless otherwise specified, equipment shall be installed per the manufacturer's specification and operated under nominal operating conditions.

Where the EUT cannot be evaluated using one or more of the test regimens specified in this standard, alternative test regimens agreed to by the manufacturer and the testing agency and accomplishing the same measurements with the same accuracy may be used. When used, the details of such alternative test regimens shall be recorded in the test report along with an explanation of why the alternative test regimen was used.

Signal injection test methods may be used to conduct tests in 5.1, 5.2, 5.3, 5.4, 5.8, and 5.10.

Several test procedures require the EUT be operated at different discrete power levels (e.g., 33%, 66%, and 100% of rated power). Adjustments may be made to the EUT to achieve the discrete power levels, provided that these adjustments do not otherwise affect the performance of the EUT for the parameter under test (PUT). Alternatively, to accomplish testing at discrete power levels, the input source may be power limited to result in the desired EUT output power levels.

IEEE Std 1547 allows for type testing to be performed on complete systems, multifunction relays, discrete devices, or any combination. If type testing is performed on anything other than a fully integrated system, some of the component times in Figure A.1 may not be available. In these cases, production and/or commissioning tests shall be conducted to fully demonstrate the ability of the complete system to comply with the timing required by IEEE Std 1547. As an alternative, that the sum of individual component timings meets the requirement may be shown in the test report.

For the purposes of this standard, multiphase ICSs include single-phase three-wire ICSs.

Copyright © 2005 IEEE. All rights reserved.

<sup>&</sup>lt;sup>6</sup>See Annex A for additional information. <sup>7</sup>See Footnote 6.

#### 5.1 Temperature stability

#### 5.1.1 Purpose

This test verifies that the EUT maintains measurement accuracy of parameters over its specified temperature range. EUT functions shall be tested to confirm that they operate within the manufacturer's stated accuracy over the stated operating temperature range. A functional test procedure to exercise each EUT input and output function shall be agreed to by the manufacturer and the testing agency. The functional test procedure shall confirm EUT operation within the manufacturer's stated accuracy for magnitude and time. It is the intent of this test to confirm the manufacturer's specified accuracy over the specified operating temperature range for measurements and timing references used to provide compliance with IEEE Std 1547.

The test consists of two sections. The operational test verifies that the EUT functions per manufacturer's specification over its operating temperature range. The storage test verifies that the EUT can be stored without damage over the manufacturer's specified storage temperature range.

Where protective, monitoring, and control functions can be conveniently separated from the ICS, the remainder of the ICS may be omitted from this test. However, the manufacturer shall provide the testing agency with substantive information to verify that the complete ICS will perform acceptably over the claimed operating temperature range.

#### 5.1.2 Procedure

#### 5.1.2.1 Operational temperature test procedure

To ensure that the equipment has reached the desired temperature, it should be allowed to stabilize at the specified chamber temperature. Stabilized temperature is reached after a minimum of 2.5 hr and when three successive temperature readings taken at 30 min intervals are within 1 °C. For the minimum operating temperature point, the equipment shall remain deengergized until the stable temperature has been achieved.

- a) Select test temperatures per the EUT specification. The EUT should be tested at the minimum, nominal (or average of maximum and minimum if not specified), and maximum operating temperatures. If nonlinear response is observed, additional test temperatures should be selected between the minimum and maximum temperatures.

- b) The trip and reset parameters to be measured over the temperature range include voltage, current, power, phase angle, frequency, and time function as appropriate for the EUT. The objective is to confirm each subsection of the EUT. The selection of parameters or functions to be evaluated for this test shall be made so that all hardware components (including those that execute software functions) likely to be affected by temperature are evaluated. Where hardware components are common to more that one function, only one of the common functions need be evaluated to confirm accuracy over the specified temperature range.

- c) Perform the tests and record the data. Perform a minimum set of tests that will verify that the EUT protective functions will operate properly over the operating temperature range as specified by the manufacturer.

- d) At each temperature point selected in step a), repeat each test selected in step b) for a total of five times.

#### 5.1.2.2 Storage temperature test procedure

Select test temperatures per the EUT specification. The EUT should be conditioned at the minimum and maximum storage temperatures. Where the EUT's operating and storage temperatures are the same, this test is not required.

Select the test method. Storage temperature performance can be established in one of two ways:

- The first method is to review the storage temperature specifications of the individual components of the EUT. If all the components meet the requirements, the EUT meets the requirements.

- The second method is to place the EUT without power for a minimum of 72 hr at each of the temperature extremes. The equipment should be returned to room temperature and proper operation should be verified.

Perform the tests and record the data.

#### 5.1.3 Criteria

#### 5.1.3.1 Operational temperature test

The EUT protective functions shall operate properly over the operating temperature range as specified by the manufacturer.

#### 5.1.3.2 Storage temperature test

The EUT shall function properly after 72 hr at the manufacturer's minimum, nominal, and maximum temperature specifications.

#### 5.1.4 Comments

It may not be necessary or feasible to temperature-test the complete EUT. Per the manufacturer's recommendation, just the components that control the parameters under test need be tested over the specified temperature range. Signal injection testing may be performed with these components per the manufacturer's recommendation.

The EUT should be arranged in the environmental chamber in such a manner that reduces, if not eliminates, opening of the chamber during testing. If the chamber must be left partially open, steps should be taken to minimize heat loss or gain. This is especially important at cold temperatures where opening of the chamber door may cause instant condensation that may affect the test. If the chamber door must be opened during test, allow sufficient time for the temperature to return to the desired test value.

If the EUT has an enclosure, it should be used especially at high temperatures to account for the additional temperature rise due to the enclosure. If including the enclosure is not practical, then the ambient temperature should be increased to a level that is agreed to by the testing agency and EUT manufacturer to account for the additional rise.

Conversely, the use of the enclosure can prevent the equipment from reaching its minimum operating temperature due to the internal rise. To account for this, the equipment should not be energized until the desired low temperature is attained or the temperature is lowered to account for the additional rise. If the manufacturer specifies a cold temperature start-up procedure, that procedure should be followed.

It is recommended that the cold temperature testing be completed first since cooling a heated chamber requires a much longer time than heating a cool chamber.

Care should be taken to mitigate condensation and frosting when performing tests after the cold soak period.

#### 5.2 Test for response to abnormal voltage conditions

If the EUT senses voltage either at the point of common coupling (PCC) with the area EPS or at the point of DR connection as specified in IEEE Std 1547, it may be tested at any convenient load level.

Copyright © 2005 IEEE. All rights reserved.

Not for Resale

If the EUT senses voltage at a different point than the PCC with the area EPS or at the point of DR connection as specified in IEEE Std 1547, it shall be tested under load in conjunction with any external isolation transformer supplied or required by the EUT manufacturer.

For a EUT that must be tested under load, these tests may be performed at an output current level convenient to the testing laboratory. When an isolation transformer is provided with or required by the EUT, IEEE 1547 compliance will be based on voltage on the area EPS side of the transformer. Testing under load shall be at both

- Its minimum operating current and

- At both unity power factor (p.f.) and the minimum DR p.f. (leading and lagging) as specified by the manufacturer at as close as possible to 100% full rated output current.

These tests shall be performed at the terminals of the EUT.

Where appropriate, signal injection test methods may be used.

#### 5.2.1 Test for overvoltage

#### 5.2.1.1 Purpose

The purpose of this test is to verify that the DR interconnection component or system ceases to energize the area EPS as specified in IEEE Std 1547 with respect to overvoltage conditions. This test determines the magnitude and trip time for each overvoltage function.

#### 5.2.1.2 Procedure—magnitude

This procedure uses the ramp function defined in Annex A.

- a) Connect the EUT according to the instructions and specifications provided by the manufacturer.

- b) Set all source parameters to the nominal operating conditions for the EUT.

- c) Set (or verify) all EUT parameters to the nominal operating settings. If the overvoltage setting is adjustable, set the EUT to the minimum overvoltage setting, but no less than the nominal voltage plus twice the manufacturer's stated accuracy.

- d) Record applicable settings.

- e) For single-phase units, adjust voltage to starting point  $V_b$ , as defined in Annex A. The source shall be held at this voltage for period  $t_h$ .<sup>8</sup> At the end of this period, initiate the ramp using the procedure specified in Annex A. For multiphase units, adjust voltage on one phase to starting point  $V_b$  and initiate the ramp using the procedure specified in Annex A. Ensure that remaining phases are held at nominal.

- f) Record all voltage magnitudes when the unit trips.

- g) Repeat steps d) through f) four times for a total of five tests.

- h) For multiphase units, repeat steps d) through g) for each phase individually and all phases simultaneously.

- i) If the trip magnitude is adjustable, repeat steps d) through h) at the midpoint and maximum of the range.

#### 5.2.1.2.1 Requirements

If used, the simulated area EPS shall meet the requirements of 4.6.1. The measurement system shall meet the requirements of 4.6.2.

<sup>&</sup>lt;sup>8</sup>The variable  $t_h$  is at least two times the trip time setting. This number may be adjusted to avoid conflict with other trip points.

If in step h) of the procedure in 5.2.1.2, the simultaneous multiphase test results vary from the individual phase test results by more than the manufacturer's specified accuracy, additional testing may be necessary to verify that the EUT is responding to phase to neutral magnitude changes instead of phase-to-phase magnitude changes.

#### 5.2.1.2.2 Criteria

The EUT shall be considered in compliance if it trips in the overvoltage range specified in IEEE Std 1547.

#### 5.2.1.3 Procedure—trip time

This procedure uses the step function defined in Annex A.

- a) Connect the EUT according to the instructions and specifications provided by the manufacturer.

- b) Set all source parameters to the nominal operating conditions for the EUT.

- c) Set (or verify) all EUT parameters to the nominal operating settings. If the overvoltage trip time setting is adjustable, set it to the minimum.

- d) Record applicable settings.

- e) Set the source voltage to a value within 10% of, but not exceeding, the overvoltage trip point setting. The source shall be held at this voltage for period  $t_{\rm h}$ .<sup>9</sup> At the end of this period, step the source voltage to a value that causes the unit to trip. Hold this value until the unit trips. For multiphase units, this test may be performed on one phase only.

- f) Record the trip time.

- g) Repeat steps d) through f) four times for a total of five tests.

- h) If the overvoltage time setting is adjustable, repeat steps d) through g) at the midpoint and maximum overvoltage time settings.

#### 5.2.1.3.1 Requirements

If used, the simulated area EPS shall meet the requirements of 4.6.1. The measurement system shall meet the requirements of 4.6.2.

#### 5.2.1.3.2 Criteria

The EUT shall be considered in compliance if the measured trip time is within the clearing time for the overvoltage range specified in IEEE Std 1547.

#### 5.2.2 Test for undervoltage

#### 5.2.2.1 Purpose

The purpose of this test is to verify that the DR interconnection component or system ceases to energize the area EPS as specified in IEEE Std 1547 with respect to undervoltage conditions. This test determines the magnitude and trip time for each undervoltage function.

#### 5.2.2.2 Procedure—magnitude

This procedure uses the ramp function defined in Annex A.

- a) Connect the EUT according to the instructions and specifications provided by the manufacturer.

- b) Set all source parameters to the nominal operating conditions for the EUT.

<sup>9</sup>See Footnote 8.

Copyright © 2005 IEEE. All rights reserved.

- c) Set (or verify) all EUT parameters to the nominal operating settings. If the undervoltage setting is adjustable, set the EUT to the minimum undervoltage setting.

- d) Record applicable settings.

- e) For single-phase units, adjust voltage to starting point  $V_b$ , as defined in Annex A. The source shall be held at this voltage for period  $t_h$ .<sup>10</sup> At the end of this period, initiate the ramp using the procedure specified in Annex A. For multiphase units, adjust voltage on one phase to starting point  $V_b$  and initiate the ramp using the procedure specified in Annex A. Ensure that remaining phases are held at nominal.

- f) Record all voltage magnitudes when the unit trips.

- g) Repeat steps d) through f) four times for a total of five tests.

- h) For multiphase units, repeat steps d) through g) for each individual phase and all phases simultaneously.

- i) If the trip magnitude is adjustable, repeat steps d) through h) at the midpoint and maximum of the range.

#### 5.2.2.2.1 Requirements

If used, the simulated area EPS shall meet the requirements of 4.6.1. The measurement system shall meet the requirements of 4.6.2.

If in step h) of the procedure in 5.2.2.2, the simultaneous multiphase test results vary from the individual phase test results by more than the manufacturer's specified accuracy, additional testing may be necessary to verify that the EUT is responding to phase-to-neutral magnitude changes instead of phase-to-phase magnitude changes.

#### 5.2.2.2.2 Criteria

The EUT shall be considered in compliance if it trips in the undervoltage range specified in IEEE Std 1547.

#### 5.2.2.3 Procedure—trip time

This procedure uses the step function defined in Annex A.

- a) Connect the EUT according to the instructions and specifications provided by the manufacturer.

- b) Set all source parameters to the nominal operating conditions for the EUT.

- c) Set (or verify) all EUT parameters to the nominal operating settings. If the undervoltage trip time setting is adjustable, set it to the minimum.

- d) Record applicable settings.

- e) Set the source voltage to a value within 10% of, but not exceeding, the undervoltage trip point setting. The source shall be held at this voltage for period  $t_h$ .<sup>11</sup> At the end of this period, step the source voltage to a value that causes the unit to trip. Hold this value until the unit trips. For multiphase units, this test may be performed on one phase only.

- f) Record the trip time.

- g) Repeat steps d) through f) four times for a total of five tests.

- h) If the undervoltage time setting is adjustable, repeat steps d) through g) at the midpoint and maximum undervoltage time settings.

<sup>&</sup>lt;sup>10</sup>See Footnote 8.

<sup>&</sup>lt;sup>11</sup>See Footnote 8.

#### 5.2.2.3.1 Requirements

If used, the simulated area EPS shall meet the requirements of 4.6.1. The measurement system shall meet the requirements of 4.6.2.

#### 5.2.2.3.2 Criteria

The EUT shall be considered in compliance if the measured trip time is within the clearing time for the undervoltage range specified in IEEE Std 1547.

#### 5.3 Response to abnormal frequency conditions

#### 5.3.1 Test for overfrequency

#### 5.3.1.1 Purpose

The purpose of this test is to verify that the DR interconnection component or system ceases to energize the area EPS as specified in IEEE Std 1547 with respect to overfrequency conditions. This test determines the magnitude and trip time for each overfrequency function.

#### 5.3.1.2 Procedure—magnitude

This procedure uses the ramp function defined in Annex A.

- a) Connect the EUT according to the instructions and specifications provided by the manufacturer.

- b) Set all source parameters to the nominal operating conditions for the EUT.

- c) Set (or verify) all EUT parameters to the nominal operating settings. If the overfrequency setting is adjustable, set the EUT to the minimum overfrequency setting.

- d) Record applicable settings.

- e) Adjust the source frequency to starting point fb. The source shall be held at this frequency for period  $t_{\rm h}$ .<sup>12</sup> At the end of this period, initiate the ramp using the procedure specified in Annex A.

- f) Record the frequency at which the unit trips.

- g) Repeat steps d) through f) four times for a total of five tests.

- h) If the overfrequency setting is adjustable, repeat steps d) through g) at the midpoint and maximum overfrequency settings.

#### 5.3.1.2.1 Requirements

If used, the simulated area EPS shall meet the requirements of 4.6.1. The measurement system shall meet the requirements of 4.6.2.

#### 5.3.1.2.2 Criteria

The EUT shall be considered in compliance if it trips in the overfrequency range specified in IEEE Std 1547.

#### 5.3.1.3 Procedure—trip time

This procedure uses the step function defined in Annex A.

a) Connect the EUT according to the instructions and specifications provided by the manufacturer.

<sup>&</sup>lt;sup>12</sup>See Footnote 8.

Copyright © 2005 IEEE. All rights reserved.

- b) Set all source parameters to the nominal operating conditions for the EUT.

- c) Set (or verify) all EUT parameters to the nominal operating settings. If the overfrequency trip time setting is adjustable, set it to the minimum.

- d) Record applicable settings.

- e) Set the source frequency to a value within 1% of, but not exceeding, the overfrequency trip point setting. The source shall be held at this frequency for period  $t_{\rm h}$ .<sup>13</sup> At the end of this period, step the source frequency to a value that causes the unit to trip. Hold this value until the unit trips.

- f) Record the trip time.

- g) Repeat steps d) through f) four times for a total of five tests.

- h) If the overfrequency time setting is adjustable, repeat steps d) through g) at the midpoint and maximum overfrequency time settings.

#### 5.3.1.3.1 Requirements

If used, the simulated area EPS shall meet the requirements of 4.6.1. The measurement system shall meet the requirements of 4.6.2.

#### 5.3.1.3.2 Criteria

The EUT shall be considered in compliance if the measured trip time is within the clearing time for the overfrequency range specified in IEEE Std 1547.

#### 5.3.1.3.3 Comments

For some EUT, the step size past the frequency trip limit should be as small as possible to reduce false results. Large frequency step changes can interfere with EUT phase lock loop operation.

#### 5.3.2 Test for underfrequency

#### 5.3.2.1 Purpose

The purpose of this test is to verify that the DR interconnection component or system ceases to energize the area EPS as specified in IEEE Std 1547 with respect to underfrequency conditions. This test determines the magnitude and trip time for each underfrequency function.

#### 5.3.2.2 Procedure—magnitude

This procedure uses the ramp function defined in Annex A.

- a) Connect the EUT according to the instructions and specifications provided by the manufacturer.

- b) Set all source parameters to the nominal operating conditions for the EUT.

- c) Set (or verify) all EUT parameters to the nominal operating settings. If the underfrequency setting is adjustable, set the EUT to the minimum underfrequency setting.

- d) Record applicable settings.

- e) Adjust the source frequency to starting point fb. The source shall be held at this frequency for period  $t_{\rm h}$ .<sup>14</sup> At the end of this period, initiate the ramp using the procedure specified in Annex A.

- f) Record the frequency at which the unit trips.

- g) Repeat steps d) through f) four times for a total of five tests.

<sup>&</sup>lt;sup>13</sup>See Footnote 8.

<sup>&</sup>lt;sup>14</sup>See Footnote 8.

h) If the underfrequency setting is adjustable, repeat steps d) through g) at the midpoint and maximum underfrequency settings.

#### 5.3.2.2.1 Requirements

If used, the simulated area EPS shall meet the requirements of 4.6.1. The measurement system shall meet the requirements of 4.6.2.

#### 5.3.2.2.2 Criteria

The EUT shall be considered in compliance if it trips in the underfrequency range specified in IEEE Std 1547.

#### 5.3.2.3 Procedure—trip time

This procedure uses the step function defined in Annex A.

- a) Connect the EUT according to the instructions and specifications provided by the manufacturer.

- b) Set all source parameters to the nominal operating conditions for the EUT.

- c) Set (or verify) all EUT parameters to the nominal operating settings. If the underfrequency trip time setting is adjustable, set it to the minimum.

- d) Record applicable settings.

- e) Set the source frequency to a value within 1% of, but not exceeding, the underfrequency trip point setting. The source shall be held at this frequency for period  $t_{\rm h}$ .<sup>15</sup> At the end of this period, step the source frequency to a value that causes the unit to trip. Hold this value until the unit trips.

- f) Record the trip time.

- g) Repeat steps d) through f) four times for a total of five tests.

- h) If the underfrequency time setting is adjustable, repeat steps d) through g) at the midpoint and maximum underfrequency time settings.

#### 5.3.2.3.1 Requirements

If used, the simulated area EPS shall meet the requirements of 4.6.1. The measurement system shall meet the requirements of 4.6.2.

#### 5.3.2.3.2 Criteria

The EUT shall be considered in compliance if the measured trip time is within the clearing time for the underfrequency range specified in IEEE Std 1547.

#### 5.3.2.3.3 Comments

For some EUT, the step size past the frequency trip limit should be as small as possible to reduce false results. Large frequency step changes can interfere with EUT phase lock loop operation.

#### 5.4 Synchronization

The purpose of the tests in this subclause is to demonstrate that the EUT will accurately and reliably synchronize to the area EPS according to the requirements of IEEE Std 1547. Separately excited induction generators shall be tested using the procedure for synchronous generators.

<sup>&</sup>lt;sup>15</sup>See Footnote 8.

Copyright © 2005 IEEE. All rights reserved.

Two basic test methods are provided:

- Method 1 verifies that a synchronization control function will cause the paralleling device to close only when key synchronization parameters are within allowable limits.

- Method 2 determines the magnitude of the synchronization startup current.

Equipment that can generate voltage independently of the area EPS and is thus capable of out-of-phase paralleling with the area EPS (e.g., a synchronous generator or inverter operating in a stand-alone mode) is tested to verify compliance of its synchronizing capability using Method 1.

Equipment that utilizes energy from the area EPS service to begin operation (e.g., an induction generator) and that may draw high current levels is tested to determine the synchronization current using Method 2. Equipment that generates a voltage inherently synchronized to the area EPS is also tested to determine the synchronization current using Method 2. This current value can then be used along with area EPS impedance at a specific location to estimate the maximum voltage fluctuation related to synchronization.

The EUT addressed in these procedures includes a wide range of capabilities, ranging from discrete components providing control and protection functions to complete generator equipment facilities. The intent of the testing requirement in this subclause is that the user identify the procedure most appropriate for the particular situation and use that procedure to validate equipment performance. IEEE Std 1547 requires that when paralleling with the area EPS, the DR should not cause excessive voltage fluctuation. Therefore, when in doubt, Method 2 should be used. Some equipment with multiple operating modes may have to be tested using both of the basic methods.

Three variations of Method 1 are provided. The first variation (5.4.1) assumes a simulated generator source and would be performed, for example, on a discrete relay or multifunction controller with synchronization control function. The second variation (5.4.2) assumes a real generator source is used. The third variation (5.4.3) is designed for testing of equipment in which the synchronizing functions cannot be switched off or the sensing voltage cannot be conveniently disconnected.

#### 5.4.1 Synchronization control function test using simulated sources (Method 1, variation 1)

#### 5.4.1.1 Purpose

The purpose of these tests is to demonstrate that interconnection equipment will synchronize to the area EPS across an open paralleling device (e.g., a power circuit breaker), within allowable limits of voltage, frequency, and phase-angle difference before the paralleling device is allowed to close. The procedure is intended for a discrete or multifunction interconnection control device that includes a synchronization function and may be used in laboratory tests with simulated generator equipment and a simulated area EPS source.

If the EUT does not include a paralleling device, the acceptability of the ICS for a specific site depends on the speed of operation of the paralleling device to be used with the EUT.

#### 5.4.1.2 Procedure

- a) Connect the EUT according to the instructions and specifications provided by the manufacturer.

- b) Connect the test equipment to monitor the paralleling device close command, the phase relationship between simulated generator output and area EPS sources, the frequency of each source, and the voltage of each source.

- c) Set simulated area EPS source to operate at nominal voltage and frequency. Record applicable settings.

- d) Demonstrate that the equipment will not close outside of the voltage acceptance range defined in IEEE Std 1547, but will close within that acceptance range. By holding the voltage and frequency of the simulated area EPS source at constant nominal values and varying the voltage of the generator source, the test will demonstrate that the EUT will not initiate closing outside of acceptable ranges of voltage and will close within acceptable ranges. The test will demonstrate that the EUT functions properly both from a low voltage that is raised to within an acceptable level and from a high voltage that is lowered to within an acceptable level. The following process may be used for testing the voltage:

- 1) Set the voltage and frequency of the area EPS source to nominal values.

- 2) Set the voltage of the simulated generator source to a level above the area EPS source voltage so that the voltage difference is outside the acceptance range, but the generator voltage is below the overvoltage trip limit of the EUT (if so equipped). The voltage difference should be at least twice the manufacturer's stated accuracy.<sup>16</sup>

- 3) Set and hold the frequency of the simulated generator source to that of the simulated area EPS so that frequency difference and phase angle<sup>17</sup> are within the limits allowed by the requirements of IEEE Std 1547. Include an allowance for EUT accuracy so that frequency and phase angle do not inadvertently keep the EUT from initiating a paralleling device closure.

- 4) Verify for a period of at least 3 min that the EUT does not initiate closing.

- 5) Gradually reduce the generator source voltage until the voltage difference is within the acceptance values of IEEE Std 1547 including an allowance for EUT accuracy. The voltage ramp rate should be controlled to allow reliable indication of the point at which paralleling device closure is initiated. A procedure for determining ramp rates is described in Annex A.

- 6) Record the voltage and frequency for the area EPS and generator sources, as well as the voltage, frequency, and phase-angle differences between the two sources at the point at which the EUT initiates paralleling device closure.

- 7) Repeat steps a) through f) four times for a total of five sets of readings.

- 8) Repeat steps a) through g) except with the initial simulated generator source voltage set at a level below the area EPS source voltage so that the voltage difference is outside the acceptance range, but the generator voltage is above the undervoltage trip limit of the EUT.

- e) Demonstrate that the equipment will not close outside of the frequency and phase-angle acceptance range defined in IEEE Std 1547, but will close within that acceptance range. By holding the voltage and frequency of the area EPS source constant and varying the frequency of the generator source, the test will demonstrate that the EUT will not initiate paralleling device closure outside of acceptable ranges of frequency difference and phase angle and will initiate paralleling device closure within acceptable ranges. The test will demonstrate that the EUT functions properly starting from both a low frequency that is raised to within an acceptable level and from a high frequency that is lowered to within an acceptable level.

- 1) Set the voltage and frequency of the area EPS source to nominal values. Set the generator source voltage to that of the area EPS.

- 2) Set the frequency of the simulated generator source to a level above the area EPS source frequency so that the frequency difference is outside the acceptance range, but the generator frequency is below the overfrequency trip limit of the EUT (if so equipped). The frequency difference should be at least twice the stated accuracy of the EUT.

- 3) Set and hold the voltage of the simulated generator source to that of the simulated area EPS so that voltage difference is within the limits allowed by the requirements of IEEE Std 1547. Include an allowance for EUT accuracy so that voltage difference does not inadvertently keep the EUT from initiating a paralleling device closure.

Not for Resale

<sup>&</sup>lt;sup>16</sup>If the EUT stated measurement accuracy is 1%, the initial voltage difference should be at least 2% greater than the allowable limit. <sup>17</sup>If the generator source frequency and utility source frequency are not identical, phase angle will periodically be within allowable limits.

- 4) Verify for a period of at least 3 min that the EUT does not initiate paralleling device closure.

- 5) Gradually reduce the generator source frequency until the frequency difference is within the acceptance values of IEEE Std 1547 including an allowance for EUT accuracy. The frequency ramp rate should be controlled to allow reliable indication of both the frequency and phase angle at which paralleling device closure is initiated. A procedure for determining ramp rates is described in Annex A.

- 6) Record the voltage and frequency for the area EPS and generator sources, as well as the voltage, frequency, and phase-angle differences between the two sources at the point at which the EUT initiates paralleling device closure.

- 7) Repeat steps a) through f) four times for a total of five sets of readings.

- 8) Repeat steps a) through g) except with the initial simulated generator source frequency set at a level below the area EPS source frequency so that the frequency difference is outside the acceptance range, but the generator frequency is above the underfrequency trip limit of the EUT.

#### 5.4.1.3 Requirements

Programmable arbitrary waveform generators (multiphase as necessary) may be used to provide simulated generator and area EPS voltage waveforms. The waveform generator will provide voltage and frequency signals in a form compatible with the EUT.

Simulated generator voltage and frequency control will come either from the EUT or, for passive devices, from a control computer programmed to provide the desired waveforms.

Equipment steady-state operating performance shall meet the manufacturer's standards for speed and voltage stability at no load for at least 15 min.

#### 5.4.1.4 Criteria

The testing shall demonstrate that the equipment complies with the requirements of IEEE Std 1547 for synchronization parameter limits.

Test results shall demonstrate that the EUT will not initiate closure out of range for any parameter during any test.

#### 5.4.1.5 Comments